AWG任意波形发生器 核心工作原理

系统架构

AWG采用分层处理架构,包含:

- 波形生成层:基于FPGA实现插值算法(如x4 sin(x)/x补偿)

- 数据转换层:高速DAC模块(16位分辨率,JESD204B接口)

- 信号调理层:宽带放大器(DC-25 GHz)与可调滤波器组

数字化波形生成模型

设目标波形函数为s(t)s(t),AWG通过以下过程实现信号重构:

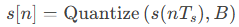

采样量化:其中Ts=1/fs为采样周期,B为DAC位数(典型值14-16 bit)

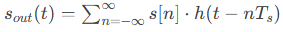

数模转换:

输出信号经DAC重建为:

h(t)为DAC重构滤波器冲击响应

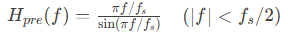

频域补偿:

为修正sin(x)/x滚降效应,需在数字域预加重:

关键性能参数分析

技术实现

多通道同步控制

量子计算等应用要求多通道AWG具备ps级同步精度:

- 时钟树设计:采用分布式PLL架构,时延偏差<200 fs

- 数字校准算法:基于互相关分析的自动时延补偿

- 测试数据:8通道AWG同步触发抖动<1.5 ps(rms)

实时波形生成技术

通过JESD204B协议实现FPGA与DAC间高速数据传输:

- 每通道数据速率:12.5 Gbps

- 协议开销:<5%(对比LVDS接口)

- 典型应用:生成5G NR 256QAM信号,误差矢量幅度(EVM)<2%

应用案例

量子比特控制

超导量子芯片操控实验表明:

- AWG生成纳秒级微波脉冲(DRAG波形)

- 相位相干性保持时间>100 μs(满足表面码纠错需求)

- 栅极保真度达99.95%(IBM Quantum实验数据)

毫米波通信测试

在28 GHz载波频段验证:

- 生成2 GHz带宽OFDM信号(PAPR=8 dB)

- ACLR(邻道泄漏比)优化至-50 dBc

- EVM性能提升30%(对比传统矢量信号源)

深圳市嘉惠捷科技有限公司

进入店铺