芯片封装工艺有哪些?

一、传统封装工艺

1. DIP(Dual In-line Package)

结构:双列直插式封装,引脚呈两排对称分布,间距2.54mm。

特点:适用于手工焊接,成本低,但引脚密度低。

应用:早期微控制器、逻辑芯片。

2. SOP/SOIC(Small Outline Package)

结构:表面贴装型,引脚从两侧引出,厚度较薄。

特点:支持SMT自动化生产,散热性能优于DIP。

应用:存储器、中低复杂度IC。

3. QFP(Quad Flat Package)

结构:四边扁平封装,引脚间距0.4-1.0mm,引脚数可达240。

特点:高密度封装,需精密贴片设备。

应用:微处理器、通信芯片。

4. PLCC(Plastic Leaded Chip Carrier)

结构:四边J形引脚,塑料封装,引脚间距1.27mm。

特点:抗机械应力强,可插座安装。

应用:工业控制芯片。

二、先进封装工艺

1. BGA(Ball Grid Array)

结构:底部焊球阵列,焊球直径0.3-0.8mm,间距0.5-1.27mm。

特点:高密度、低电感,但返修难度大。

应用:CPU、GPU、FPGA。

2. QFN(Quad Flat No-leads)

结构:无引脚四边扁平封装,底部焊盘与散热片一体。

特点:体积小、散热佳,适合高频应用。

应用:射频芯片、电源管理IC。

3. CSP(Chip Scale Package)

结构:封装尺寸≤1.2倍芯片尺寸,厚度<1mm。

特点:超薄设计,电气性能接近裸片。

应用:移动设备传感器、存储器。

4. WLP(Wafer Level Package)

工艺:直接在晶圆上完成封装,切割后即为成品。

特点:成本低、体积小,但散热能力有限。

变体:FIWLP(扇入型)、FOWLP(扇出型)。

5. 3D封装

技术:TSV(硅通孔)垂直互联,堆叠多层芯片。

特点:缩短互连长度,提升带宽,但热管理复杂。

应用:HBM存储器、AI加速芯片。

三、关键工艺流程

1.前道工艺

减薄:晶圆厚度从700μm减至50-100μm。

划片:激光或刀片切割晶圆为单颗芯片。

贴片:银胶或共晶焊将芯片固定于基板。

2.互连工艺

引线键合:金线/铜线连接芯片与基板,线径15-50μm。

倒装焊:芯片正面焊球直接连接基板,用于BGA/CSP。

3.后道工艺

塑封:环氧树脂模压保护芯片,温度170-180℃。

电镀:引脚浸锡或镀镍/金,提升焊接可靠性。

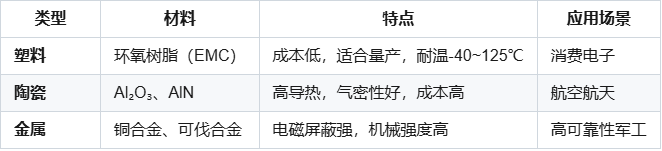

四、材料分类

五、技术趋势

异质集成:通过RDL(重布线层)实现多芯片异构封装。

面板级封装:使用更大面板替代晶圆,降低成本(FOPLP)。

嵌入式封装:将芯片埋入基板内部,减少厚度(如eWLB)

深圳市闻达讯仪器科技有限公司

进入店铺